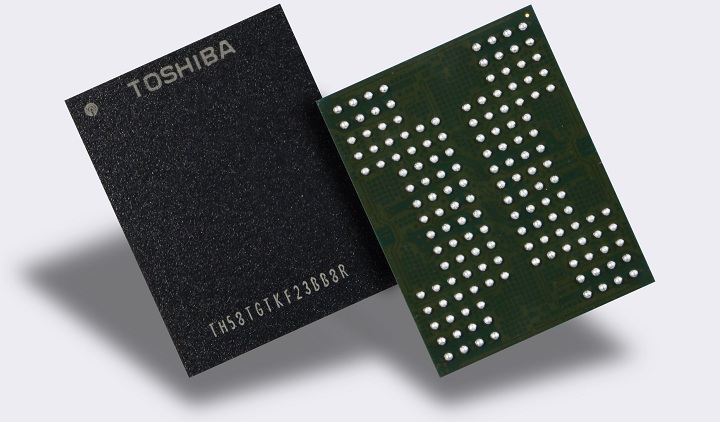

Toshiba анонсировала флеш-память 3D NAND с четырьмя битами на ячейку

Toshiba Memory Corporation и Western Digital сообщают о завершении работы над четвёртым поколением флеш-памяти BiCS (Bit-Cost-Scaling), допускающего создание 96-слойных чипов. Первые 256-гигабитные микросхемы TLC NAND, выполненные по новой технологии, начнут поступать OEM-партнёрам компаний уже во второй половине текущего года, а старт их массового производства запланирован на следующий год.

Что важно, микросхемы BiCS4 будут доступны в вариантах не только с тремя (TLC), но и четырьмя битами на ячейку (QLC), что позволит дополнительно нарастить плотность хранения информации. В частности, 64-слойный прототип 3D QLC NAND характеризуется ёмкостью 768 Гбит (96 Гбайт). При этом допускается объединение таких 16 кристаллов в одном корпусе, что позволяет создавать микросхемы флеш-памяти с рекордным объёмом в 1,5 терабайта. Образцы подобных чипов будут демонстрироваться на конференции Flash Memory Summit, которая пройдёт с 7 по 10 августа в Санта-Кларе.

Отметим, что хотя микросхемы 3D QLC NAND будут отличаться более низкой стоимостью по сравнению с решениями TLC или MLC, они допускают меньшее число перезаписей, чем более дорогие аналоги. Таким образом, новые чипы найдут применение в самых бюджетных твердотельных накопителях или устройствах большого объёма, используемых для архивного хранения информации.

Источник:

Toshiba